We went on a trip to Nasushiobara, Tochigi. We visited Minamigaoka Dairy and climbed Mt. Chausudake.

Alumni visit the laboratory

Mr. Lih and Mr. Chen, who used to stay at the Ishikuro Laboratory as exchange students from Taiwan, visited the laboratory .

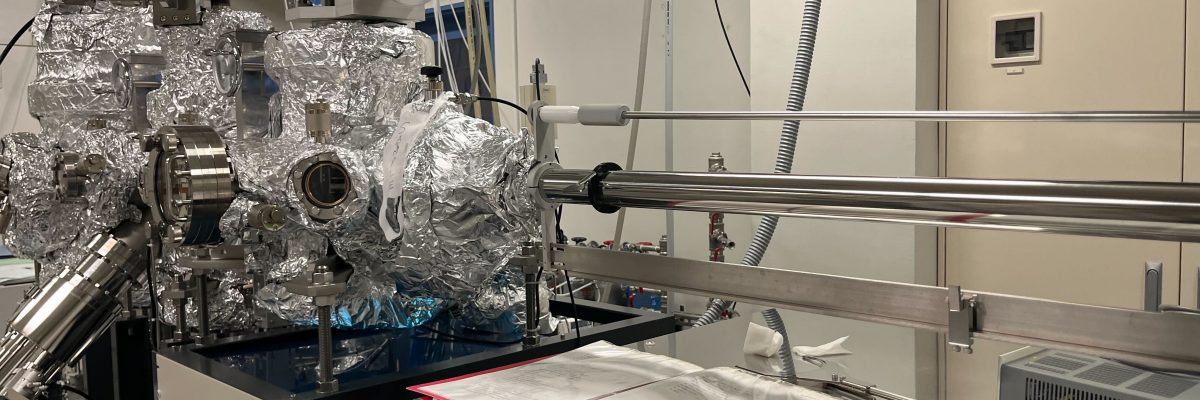

Visiting to Nagoya University

We visited to Fujimaki Laboratory, Nagoya University (Nagoya, Aichi). We had a technical review meeting on superconductive wiring.

Welcome party for Daniel from Technische Universität Braunschweig

We held a welcome party for Daniel from Technische Universität Braunschweig, Germany. He stayed 3 weeks at our laboratory.

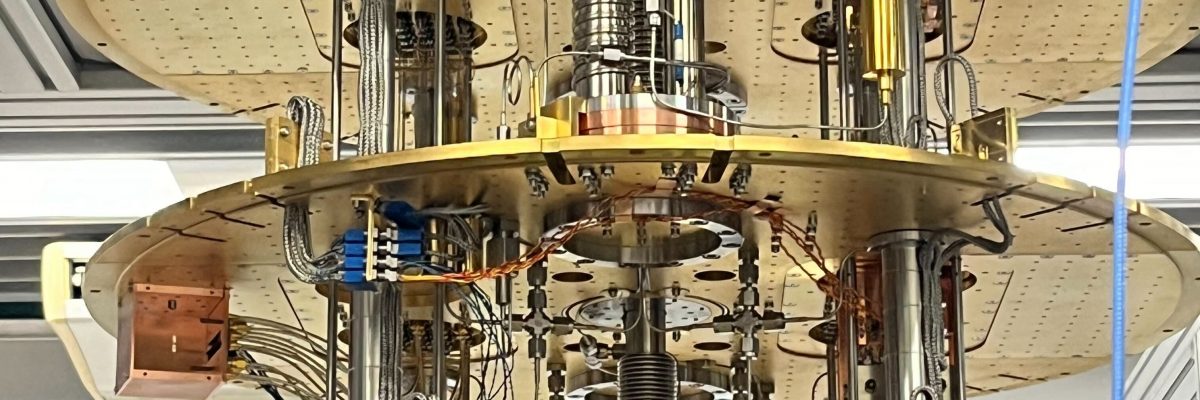

Visiting to AIST

Farewell Party for the graduates

Design of Dual Lower Bound Hysteresis Control in Switched-Capacitor DC–DC Converter for Optimum Efficiency and Transient Speed in Wide Loading Range for IoT Application

Y. Tan, C. Huang and H. Ishikuro, “Design of Dual Lower Bound Hysteresis Control in Switched-Capacitor DC–DC Converter for Optimum Efficiency and Transient Speed in Wide Loading Range for IoT Application,” in IEEE Journal of Solid-State Circuits

T/R Switch Composed of Three HV-MOSFETs With 12.1-μW Consumption That Enables Per-Channel Self-Loopback AC Tests and −18.1-dB Switching Noise Suppression for 3-D Ultrasound Imaging With 3072-Ch Transceiver

Shinya Kajiyama, Yutaka Igarashi, Toru Yazaki, Yusaku Katsube, Takuma Nishimoto, Tatsuo Nakagawa, Yohei Nakamura, Yoshihiro Hayashi, Takuya Kaneko, Hiroki Ishikuro, and Taizo Yamawaki, “T/R Switch Composed of Three HV-MOSFETs With 12.1-μW Consumption That Enables Per-Channel Self-Loopback AC Tests and −18.1-dB Switching Noise Suppression for 3-D Ultrasound Imaging With 3072-Ch Transceiver,” IEEE Transactions on Very Large […]

A Switched-Capacitor DC-DC Converter with > 77.3% Efficiency and 80 ns Active Transient Response in 40 μA – 4 mA Load Current Range

Yi Tan and Hiroki Ishikuro, “A Switched-Capacitor DC-DC Converter with > 77.3% Efficiency and 80 ns Active Transient Response in 40 μA – 4 mA Load Current Range,” IEEE 47th European Solid-State Circuits Conference (ESSCIRC), Sept. 13-17, 2021.

A Fast Wake-Up and High Accuracy Sensor Interface by Synchronous Sampling with Power-Efficient Switching Regulator

Yuya Fuketa, Kohei Tatehora, Yohsuke Shiiki, Shuya Nakagawa, and Hiroki Ishikuro, “A Fast Wake-Up and High Accuracy Sensor Interface by Synchronous Sampling with Power-Efficient Switching Regulator,” 2021 IEEE 64th International Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 9-11, 2021.